Financial Services

Algorithmic trading is changing the rules of the game

In today’s world of algorithm-driven, high-frequency trading, millions of shares can be traded in a nanosecond and any delay can cost millions. Financial trading is becoming increasingly dependent on the performance of the networks it utilizes. The inability to detect and control latency can be devastating for both investor confidence in markets and trading performance. Our SmartNICs enable you to replay captured data with nanosecond precision at line speed to continually optimize trade algorithms by measuring performance of previous trading days and testing against previous trading data.

Capture 100% of all packets for analysis

Financial information providers depend on the transport of critical market data with the lowest delay possible – without compromising delivery. To ensure that trading runs smoothly, it is crucial that exchanges, institutions, and service providers capture all network traffic, including microbursts and data gaps, which otherwise may cause misplaced or even dropped orders. Our SmartNICs capture all packets up to 100 Gbps – with guaranteed 100% zero packet loss – and accelerate data delivery to homegrown, commercial or open-source applications for further analysis.

Learn how FPGA SmartNICs help to improve the performance of trading algorithms, ensure regulatory compliance, and protect against security events.

Learn how Velocimetrics and Napatech enabled a global tier 1 Investment Bank to reduce its tick-to-trade latency from 100 μs to 10 μs.

Application

Latency Measurement

Our SmartNICs deliver data to applications to visualize delays by capturing all transactions and measuring the exact time of each event down to the nanosecond. This enables financial institutions to guarantee optimal performance and transparency of their trading infrastructure.

Fraud Detection & Regulatory Compliance

Our SmartNICs deliver data to applications to ensure compliance with regulations, protect trading information, and reduce the risk of confidential information leaks. This enables stock exchanges to provide a seamless, secure trading experience for their customers.

Products

Address key industry challenges with Napatech products.

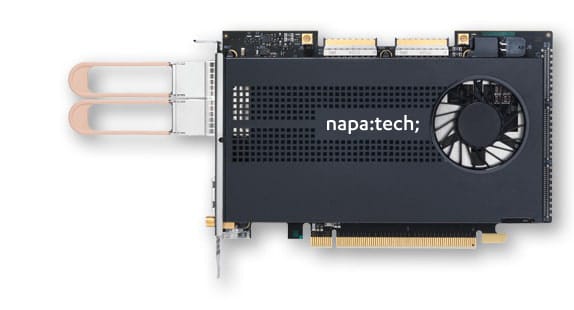

Napatech FPGA SmartNICs

- 1-200G

- 100% PACKET CAPTURE

- COTS

- NEBS

- PLUG & PLAY

Napatech FPGA SmartNICs capture data from networks at high speed and high volume using patented packet capture technology. With a portfolio that scales from 1 to 100G, we provide faster, more efficient data delivery and enable real-time insight into network traffic.