F2070X Data Processing Unit (DPU)

2×10/25G, 8×10/25G, 2x100G

Powerful Intel®/Altera®-based Data Processing Unit (DPU)

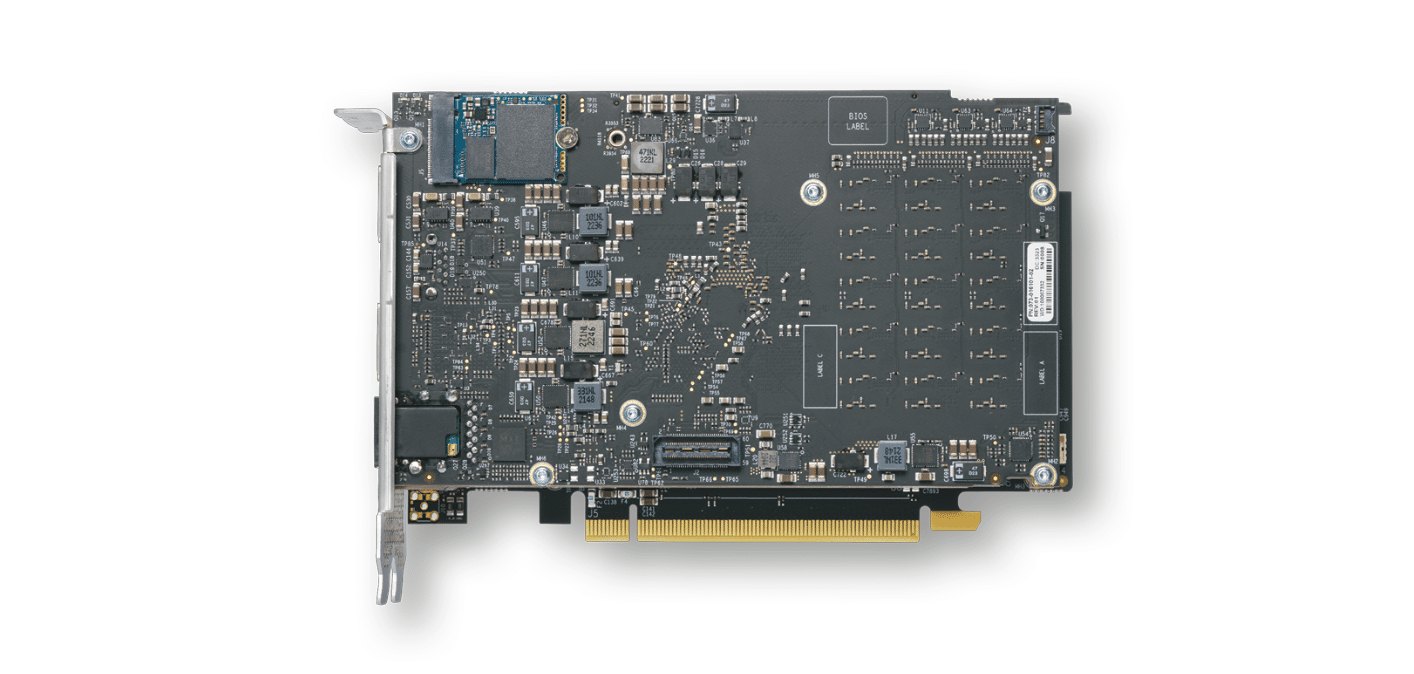

The Napatech F2070X Data Processing Unit (DPU) is a 2x100Gbe PCIe card with an Agilex™ AGFC023 FPGA and an Intel® Xeon® D SoC. The unique combination of FPGA and full-fledged Xeon CPU on a PCI card allows for unique offload capabilities. Coupled with Napatech software, the F2070X is the perfect solution for network, storage and security offload and acceleration. It enables virtualized cloud, cloud-native or bare-metal server virtualization with tenant isolation.

Customization on demand

The F2070X uniquely offers both programmable hardware and software, to tailor the DPU to the most demanding and specific needs in your network, and to modify and enhance its capabilities over the life of the deployment. It is based on the Intel Application Stack Acceleration Framework (ASAF) that supports the integration of software and IP from Intel, Napatech, 3rd parties and homegrown solutions. This one of a kind architecture enables hardware performance and the speed of software innovation.

Scalable platform

The Napatech F2070X comes in a standard configuration, and includes support for several combinations of Altera® FPGAs, Intel® Xeon® D processors, and memory. This enables tailored platform configurations matching requirements for specific use cases.

Compatible Software

![]()

Link-Storage™ Software

Maximizes the performance of data center storage based on NVME over TCP (NVME/TCP).

![]()

Link-Security™ Software

Maximizes the performance of data center security based on Transport Layer Security (TLS) encryption.

![]()

Link-Virtualization™ Software

Maximizes the performance of data center networking for Infrastructure-as-a-Service platforms.

![]()

Link-Programmable™ Software

Link-Programmable™ enables end users and OEMs to deploy their own FPGA IP on Napatech’s industry-proven SmartNIC platform.

Watch video by NextGenInfra where Charlie Ashton, Senior Director of Business Development from Napatech explains how

Data Processing Units (DPUs) promise big gains in efficiency for data center operations.

F2070X DPU

Compliance

Napatech upholds the highest quality, environmental and safety standards, and complies with all applicable regulations across regions. This helps our customers to realize a seamless integration without delays – and ensures error-free operation throughout the product life cycle.

Ethernet Front Port Compliance

The DPU design maximizes mechanical and electrical front port margin, securing trouble-free operation with the optical or electrical modules of the customer’s choice.

The thermal design is validated dissipating the maximum power level as standardized for the given form factor. Margin on the data interface has been optimized tuning the equalization parameters of the transceivers hosting the front port channel, maximizing EYE margin to the relevant standard.

EMC Compliance

All Napatech designs have passed EMC compliance testing for major regions, including Europe and North America. By ensuring compliance as an integral part of the design, the risk of delays is eliminated. Moreover, the EMC testing has been performed in a mainstream server, potentially directly applicable to the use case.

Environmental Compliance

The end product (server + installed DPU) must adhere to regional environmental legislation. To enable trouble-free server integration, Napatech DPUs are manufactured using only materials that fully comply with the current RoHS, REACH and proprietary Tier 1 legislation.

Full compliance from early inception eliminates the risk delays and product withdrawal due to authority intervention.

Event Handling & System Monitoring

In order for the DPU to become an integral part of the server environment and maximize uptime, it needs to monitor and expose key performance metrics to the application during operation. Napatech DPUs monitor the following metrics:

- Hot spot temperatures

- Key supply voltages and currents

- PCI protocol events

- General system events

PCI Compliance

With the PCI interface on the DPU dictated by the server plane, the hardware maximizes mechanical and electrical PCI margin, ensuring trouble-free operation in the server and server slot(s) of the customer’s choice. All designs have passed relevant PCI-SIG tests and have been adopted on the PCI-SIG integrators list.

Safety Compliance

To enable trouble-free server integration, Napatech DPUs are fully compliant with all applicable safety standards.

By ensuring safety compliance as an integral part of the DPU design, the risk of delays is eliminated. Compliance testing is performed in a mainstream server, potentially directly applicable to the use case.

Conflict Minerals Compliance

To ensure quick and trouble-free server integration, Napatech DPUs are manufactured using only materials that fully comply with the relevant Conflict Mineral Legislation. For US based DPU integrators, this facilitates submission of the mandatory Conflict Mineral report to SEC.

Shock & Vibration Robustness

Many server environments expose the DPU to substantial shock and vibration, predominantly during the transportation phase. To ensure trouble-free server integration and operational robustness throughout the product life cycle, validated design aspects include:

- Cooling enclosure for superior mechanical stiffness

- Key exposed components are under-filled (glued) to the PCB

- Shock robustness validated against JESD22-B110A

- Vibration robustness validated against ASTM D4169-09

Feature Highlights and Specifications

| FPGA Device and Memory |

|

| SoC Processor and Memory |

|

| PCI Express Interfaces |

|

| Front Panel Network Interfaces |

|

| Supported Compute and Memory Devices (Mount Options) |

|

| Size |

|

| Power and Cooling |

|

| Time Synchronization (Mount Options) |

|

| Board Management |

|

| SoC Processor Operating System |

|

| Supported Host Processor Operating Systems |

|

| Environment and Approvals |

|

| Application Stack Acceleration Framework (ASAF) |

|

| Open vSwitch (OVS) Offload |

|

| Storage Offload |

|

| Security Offload |

|

| Supported Hardware and Transceivers |

|