![]()

Link-Inline™ Software

for Napatech FPGA-based SmartNICs

Napatech SmartNICs and Link-Inline™ Software provide a hardware-based solution for accelerating network and security applications dramatically increasing application performance while reducing CPU consumption. The Link-Inline™ Software provides a processing architecture which offloads and accelerates flow aware application dataplanes offering the ability to scale open source and custom applications to >100 Gbps in standard servers with lower complexity and enhanced scalability than alternatives.

Link-Inline™ Software supports a broad range of applications and use cases – and can immediately improve an organization’s ability to scale critical networking use cases.

Key Benefits

Napatech provides the unique combination of the industries highest performance FPGA-based SmartNIC with software for offload and accelerate Inline networking and security applications.

![]()

High Performance

Scale network and security applications to 100Gbps

![]()

Low Latency

Minimize network delays for inline applications

![]()

Significantly Reduced CPU Utilization

Return CPU cores to applications and services

![]()

Total Cost of Ownership

Cost effective scaling for your data center

![]()

Reconfigurability

Completely programmable for custom requirements

![]()

Environmentally Sound

Lower power, space, and cooling

Key Features

Napatech Link-Inline™ Software provides the Napatech SmartNIC family with a robust feature set and extendable architecture allowing configurable, flow-based offload and acceleration for networking and security applications.

![]()

Stateful Flow Processing

![]()

200 Gbps Throughput

![]()

2 Million Flow setups / second

![]()

100 million flow table entries

![]()

Inline, Packet Capture, or Tap modes

![]()

Configurable packet classification / match fields

![]()

Extensive actions

![]()

Load balancing to application instances

Cyber Security Processing Challenges

Networking and cybersecurity applications and services are often deployed as software in high volume, low-cost standard servers. Many, however, require higher throughput and lower latency than can be provided by compute platforms with basic network interface cards (NICs).

Napatech’s Link-Inline™ software and SmartNIC hardware provides the ability to scale open source and custom networking and security applications to >100 Gbps in standard servers. This stateful, flow-aware solution allows applications running in software to dynamically and programatically update processing actions in SmartNIC hardware on a per flow basis, tightly coupled with the application via simple to use rules or standards-based APIs. The solution scales to greater than 100 million flows, each monitored in a stateful manner with over 2 million flow setups and teardowns per second with low latency.

To find out more see:

Link-Inline™ Software Product Brief

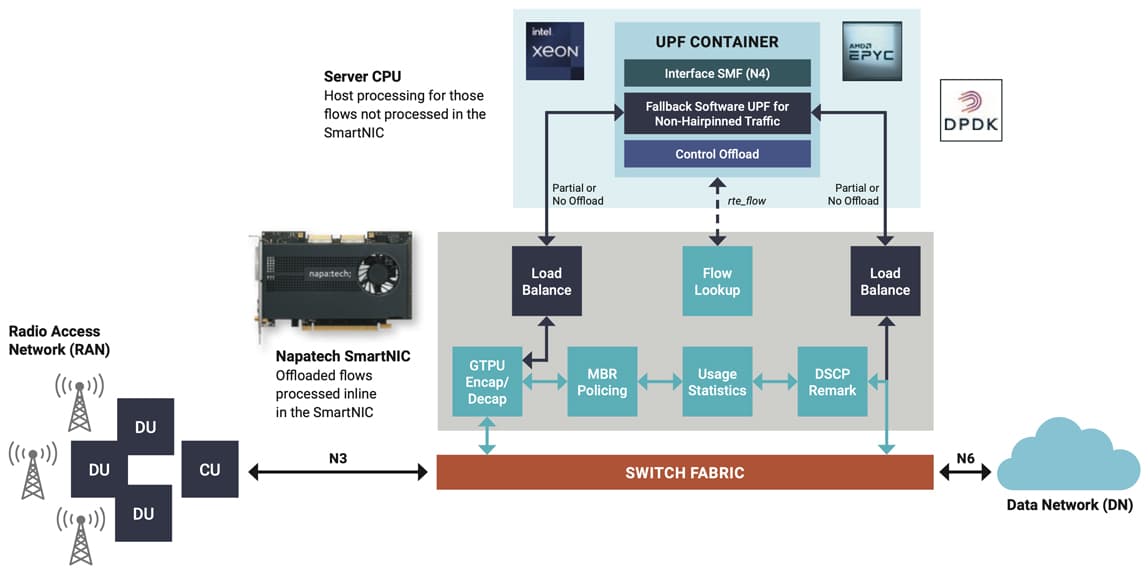

5G Telecom User Plane Traffic Challenges

As Communications Service Providers and enterprises scale up the deployment of their 5G networks, it becomes critical to optimize the Return on Investment for their infrastructure. With 5G User Plane Function (UPF) representing a significant part of the overall workload for the 5G Packet Core, it’s important to leverage solutions that maximize the number of users supported per server and thereby minimize the overall cost per user.

By offloading the UPF data plane processing from the server CPU to an integrated hardware/software SmartNIC solution, Napatech delivers industry-leading performance for the UPF function. This offload solution is based on industry- standard APIs and cloud-native orchestration, enabling it to be easily integrated into complete 5G Core products offered by telecom software vendors.

To find out more see:

5G User Plane Function (UPF) Offload Data Sheet

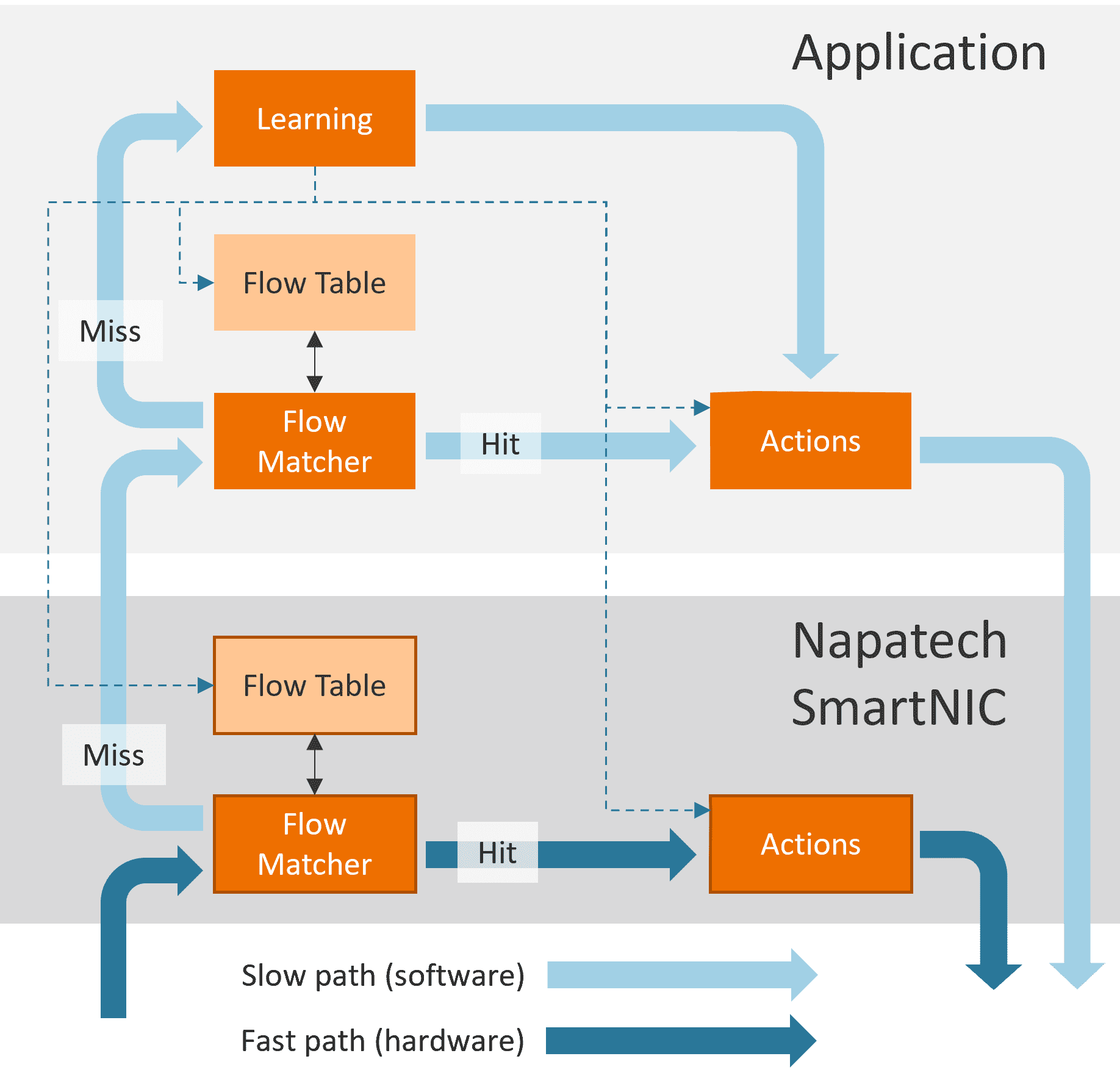

Stateful Flow Management and Offload

To maintain performance at high speeds and address all of these challenging issues, Link-Inline™ software offloads packet and flow-based processing to reconfigurable FPGA-based SmartNICs. The SmartNIC performs flow classification and identification on ingress and maintains state for each packet of a flow. For known flows, action processing is dynamically handled completely in the SmartNIC and all other packets are forwarded to the application for additional analysis to minimize the load on user-space applications. Link-Inline™ Software additionally provides the ability to dynamically identify and direct data flows into specific CPU cores based on the type of traffic being analyzed. Link-Inline™ software is tightly coupled to x86 cores for inline network and security applications. Per-flow match/action processing in HW gives control back to the user providing additional computation to the application by reducing the amount of data needed for processing as certain flows or protocols that no longer need monitoring and can be blocked or forwarded in hardware.

Napatech’s Link-Inline™ software accelerates standard Linux applications and provides open APIs for development and integration of inline network applications. The solution significantly reduces host CPU utilization and solution latency by offloading complex flow classification and packet processing to the SmartNIC.

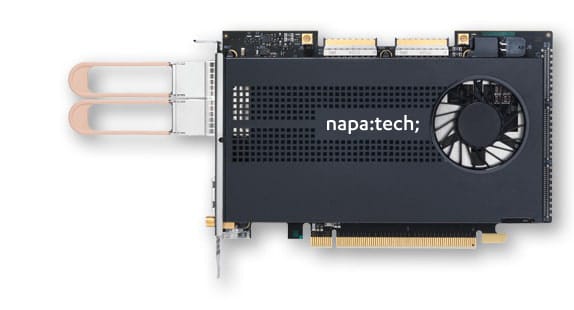

Compatible Napatech FPGA-based SmartNICs

The Link-Inline™ Software is available for our family of FPGA-based SmartNICs.

NT200A02 SmartNIC

2x100G

The NT200A02 SmartNIC is a full height, half length QSFP28 PCIe card based on a powerful FPGA-based architecture which enables 8x10G, 2×10/25G, 4×10/25G, 2x40G or 2x100G applications.

These SmartNICs offer flexibility to create high-performance solutions in server platforms for supporting network infrastructures up to 100G and can be reconfigured to support specific SmartNIC functionality. They are available in both a self-contained cooling and passive cooling version.

Tech specs

| FEATURES | Link-Inline™ Software for Napatech FPGA SmartNICs |

| Stateful flow management |

|

| Pre-filtering |

|

| CPU load distribution |

|

| Rx Packet Processing |

|

| Tx Packet Processing |

|

| Advanced Statistics |

|

| Monitoring Sensors (*) |

|

| Supported OS and Orchestration |

|

| Supported APIs |

|

| Supported Hardware and Transceivers |

|