Napatech Link-Inline™ Software

for Napatech FPGA-based SmartNICs

Product Brief

5G Telecom User Plane Traffic Challenges

As Communications Service Providers and enterprises scale up the deployment of their 5G networks, it becomes critical to optimize the Return on Investment for their infrastructure. With 5G User Plane Function (UPF) representing a significant part of the overall workload for the 5G Packet Core, it’s important to leverage solutions that maximize the number of users supported per server and thereby minimize the overall cost per user.

By offloading the UPF data plane processing from the server CPU to an integrated hardware/software SmartNIC solution, Napatech delivers industry-leading performance for the UPF function. This offload solution is based on industry-standard APIs and cloud-native orchestration, enabling it to be easily integrated into complete 5G Core products offered by telecom software vendors.

Cyber Security Processing Challenges

Network security architects are seeing requirements for their solutions quickly changing with the explosion in network throughputs while at the same time, the threat landscape is continuously evolving and becoming more complex and sophisticated. Stateless security solutions are no longer adequate to identify and block threats. Inline networking and security solutions require complete and stateful awareness of all users and applications at throughputs topping 200Gbps.

To support these requirements, network infrastructures need to contain more intelligence with deeper inspection of traffic at increasing line rates. With this need for inline stateful flow processing, application awareness, content inspection, and security processing, the amount of compute power to meet these increasing line rates grows exponentially.

Stateful Flow Management and Offload

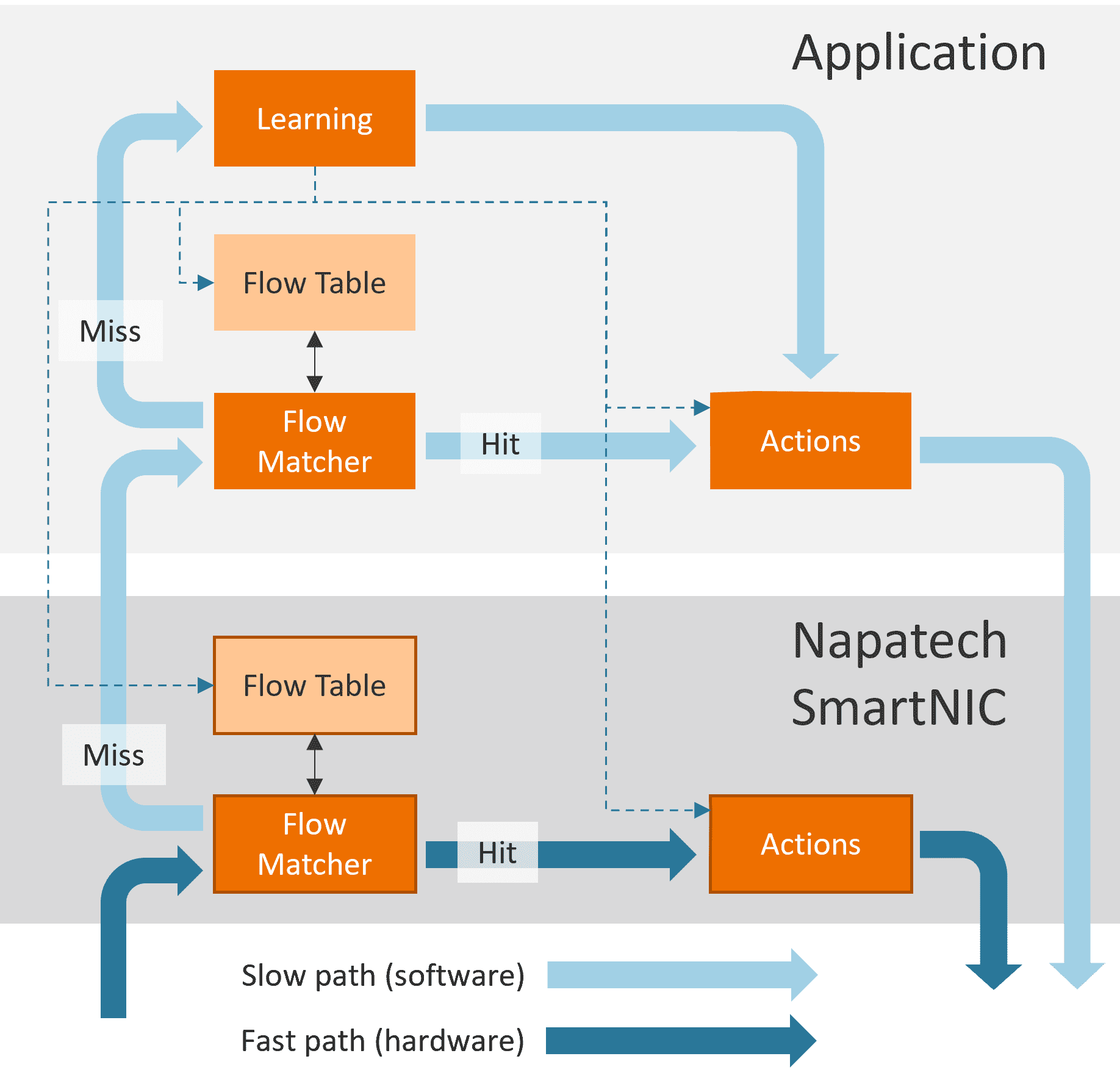

To maintain performance at high speeds and address all of these challenging issues, Link-Inline™ software offloads packet and flow-based processing to reconfigurable FPGA-based SmartNICs. The SmartNIC performs flow classification and identification on ingress and maintains state for each packet of a flow. For known flows, action processing is dynamically handled completely in the SmartNIC and all other packets are forwarded to the application for additional analysis to minimize the load on user-space applications. Link-Inline™ Software additionally provides the ability to dynamically identify and direct data flows into specific CPU cores based on the type of traffic being analyzed. Link-Inline™ software is tightly coupled to x86 cores for inline network and security applications. Per-flow match/action processing in HW gives control back to the user providing additional computation to the application by reducing the amount of data needed for processing as certain flows or protocols that no longer need monitoring and can be blocked or forwarded in hardware.

Napatech’s Link-Inline™ software accelerates standard Linux applications and provides open APIs for development and integration of inline network applications. The solution significantly reduces host CPU utilization and solution latency by offloading complex flow classification and packet processing to the SmartNIC.

Stateful Flow Management Block Diagram

| FEATURES | Link-Inline™ Software for Napatech FPGA SmartNICs |

| Stateful flow management |

|

| Pre-filtering |

|

| CPU load distribution |

|

| Rx Packet Processing |

|

| Tx Packet Processing |

|

| Advanced Statistics |

|

| Monitoring Sensors (*) |

|

| Supported OS and Orchestration |

|

| Supported APIs |

|

| Supported Hardware and Ports Speeds |

|

![]()